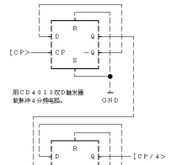

在电子技术中,N/2(N为奇数)分频电路有着重要的应用,对一个特定的输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。CD4013是双D触发器,在以CD4013为主组成的若干个二分频电路的基础上,加上异或门等反馈控制,即可很方便地组成N/2分频电路。CD4013由两个相同的、相互独立的数据型触发器构成。每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出。此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计数器和触发器。在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

1D、2D:数据输入端

1CP、2CP:时钟输入端1Q、2Q:原码输出端1 /Q、2 /Q:反码输出端

dzsc/19/4011/19401155.jpg

1SD、2SD:直接置位端

1RD、2RD:直接复位端

VDD:电源正

VSS:地

CD4013有两个D触发器,一个D触发器有6个端子:2个输出,4个控制。4个控制分别是R、S、CP、D。

1)R和S不能同时为高电平。

2)当R为1、S为0时,输出Q一定为0,因此R可称为复位端。

3)当S为1、R为0时,输出Q一定为1。

4)当R、S均为0时,Q在CP端有脉冲上升沿到来时动作,具体是Q=D,即若D为1则Q也为1,若D为0则Q也为0。

RD(复位端)

SD(置位端)

Q(输出端)

1

0

0

0

1

1

0

0

D

1

1

x

设电路初始状态均在复位状态,Q1、Q2端均为低电平。当fi信号输入时,由于输入端异或门的作用(附表是异或门逻辑功能表),其输出还受到触发器IC2的Q2端的反馈控制(非门F2是增加的一级延迟门,A点波形与Q2相同)。在第1个fi时钟脉冲的上升沿作用下,触发器IC1、IC2均翻转。由于Q2端的反馈作用使得异或门输出一个很窄的正脉冲,宽度由两级D触发器和反相门的延时决定。当第1个fi脉冲下跳时,异或门输出又立即上跳,使IC1触发器再次翻转,而IC2触发器状态不变。这样在第1个输入时钟的半个周期内促使IC1触发器的时钟脉冲端CL1有一个完整周期的输入,但在以后的一个输入时钟的作用下,由于IC2触发器的Q2端为高电平,IC1触发器的时钟输入跟随fi信号(反相或同相)。本来IC1触发器输入两个完整的输入脉冲便可输出一个完整周期的脉冲,现在由于异或门及IC2触发器Q2端的反馈控制作用,在第1个fi脉冲的作用下得到一个周期的脉冲输出,所以实现了每输入一个半时钟脉冲,在IC1触发器的Q1端取得一个完整周期的输出。

图3是5/2分频电路。IC1、IC2、IC3三级D触发器级联为8分频电路,电容C起滤波作用,输出信号fo从IC2的Q2端输出。电路中有Q1、Q3两个反馈控制。从图4工作波形可知,Q1的反馈信号中每两个反馈信号中就有一个受到Q3反馈波形的影响,所以在A点仅能形成几百毫微秒宽的脉冲。由于电容C的作用,Q1的反馈信号(即一窄脉冲)被滤除掉,如图4波形A的虚线所示。在Q2端输出fo信号。fo每变化一个周期,对应于输入信号fi的两个半周期,即fo的频率为fi的2/5。

图5是7/2分频电路。该电路与图3相似,区别在于电路中一个反馈信号在图3中是从Q1端引出的,而图5是从Q2端引出的,fo信号从Q2端输出。电路有Q2、Q3两级反馈,由于Q2反馈信号受Q3反馈的影响,在A点仅能形成几百毫微秒宽的窄脉冲,此窄脉冲被电容C滤除掉,因此Q2反馈不起作用,电路实际上只有一个Q3反馈,因而使得fo输出信号每变化一个周期,对应于fi输入信号的三个半周期,即fo的频率为fi的2/7。其工作波形如图6所示。

上面介绍的N/2分频电路仅限于N≤7,当N≥7时,可根据分频N值的大小,相应增加二分频级数,并恰当引接反馈信号走线,便可得到N≥7的分频电路。下面仅介绍一例9/2分频电路,如图7所示。图8是其工作波形。

IC1~IC4四级D触发器组成16分频电路,fo信号从Q3输出,电路有Q1、Q4两级反馈。其工作原理与上述有关分频电路相似,波形图上A点虚线脉冲表示为电容C滤除掉的Q1反馈信号。从图8中可知,只要fi输入四个半周期的时钟信号,就输出一个周期信号fo,即fo的频率为fi的2/9。

从以上几个N/2分频电路可得到如下几个特性:

1.电路工作原理是,在第n个周期,末级两分频器的输出为高电平时,输入时钟脉冲的上升沿使分频电路工作;在第n+1个周期,末级两分频器的输出为低电平时,输入时钟脉冲的下降沿使分频电路工作。

2.电路采用的是异步触发形式,各触发器的初始状态不会影响到分频的功能。如果要求初始状态为“0”状态,可以将D触发器的复位端R引出,接至复位控制电路。

3.输入信号fi的工作频率fimax除受到CMOS元件fM的限制外,还受到D触发器、反馈门翻转延迟和电容C滤波频率特性的影响,所以应尽可能提高fi的值。一般情况下,工作频率fimax在几百千赫以下。用CD4013双D触发器做的脉冲4分频器

dzsc/19/4011/19401155.jpg

供应 STC12C5628AD 宏晶单片机

信息内容:单片机诞生于1971年,经历了SCM、MCU、SoC三大阶段,早期的SCM单片机都是8位或4位的。其中最成功的是INTEL的8031,此后在8031上发展出了MCS51系列MCU系统。基于这一系统的单片机系统直到现在还在广泛使用。随着工业控制领域要求的提高,开始出现了16位单片机,但因为性价比不理想并未得到很广泛的应用。90年代后随着消费电子产品大发展,单片机技术得到了巨大提高。随着INTEL i960系列特别是后来的ARM系列的广泛应用,32位单片机迅速取代16位单片机的高端地位,并且进入主流市场。 而传统的8位单片机的性能也得到了飞速提高,处理能力比起80年代提高了数百倍。高端的32位Soc单片机主频已经超过300MHz,性能直追90年代中期的专用处理器,而普通的型号出厂价格跌落至1美元,端的型号也只有10美元。 当代单片机系统已经不再只在裸机环境下开发和使用,大量专用的嵌入式操作系统被广泛应用在全系列的单片机上。而在作为掌上电脑和手机核心处理的高端单片机甚至可以直接使用专用的Windows和Linux操作系统。 主要阶段 早期阶段 SCM即单片微型计算机(Single Chip Microcomputer)阶段,主要是寻求的单片形态嵌入式系统的体系结构。“创新模式”...

供应 A3955SBT 电源驱动IC

信息内容:Allegro是Cadence推出的先进 PCB 设计布线工具。 Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品Cadence、OrCAD、Capture的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。 dzsc/19/4011/19401159.jpg 外国Allegro网站图片 Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。 软件中的 Constraint Manger 提供了简洁明了的接口方便使用者设定和查看 Constraint 宣告。它与 Capture 的结合让 E.E. 电子工程师在绘制线路图时就能设定好规则数据,并能一起带到Allegro工作环境中,自动在摆零件及布线时依照规则处理及检查,而这些规则数据的经验值均可重复使用在相同性质的电路板设计上。 Allegro 除了上述的功能外,其强大的自动推挤 push 和贴线 hug 走线以及完善的自动修线功能更是给用户提供极大的方便;强大的贴图功能,可以提供多用户同时处理一块复杂板子,从而大大地提高了工作效率。或是利...