说明

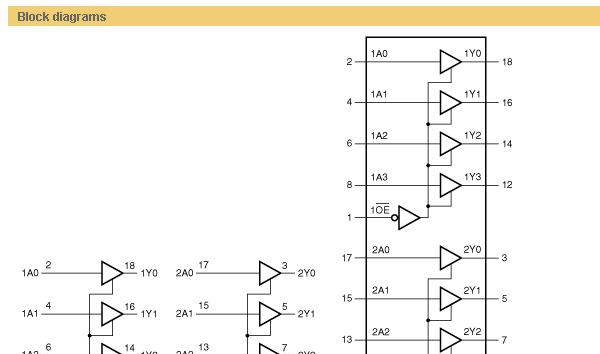

These octal buffers and line drivers are designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The ’HC244 devices are organized as two 4-bit buffers/drivers with separate output-enable (OE)\ inputs. When OE\ is low, the device passes noninverted data from the A inputs to the Y outputs. When OE\ is high, the outputs are in the high-impedance state.

特性

- Wide Operating Voltage Range of 2 V to 6 V

- High-Current Outputs Drive Up To 15 LSTTL Loads

- 3-State Outputs Drive Bus Lines or Buffer Memory Address Registers

- Low Power Consumption, 80-µA Max ICC

- Typical tpd = 11 ns

- ±6-mA Output Drive at 5 V

- Low Input Current of 1 µA Max

dzsc/17/6600/17660024.jpg

供应三态输出的八路缓冲器和线路驱动器74HC244N

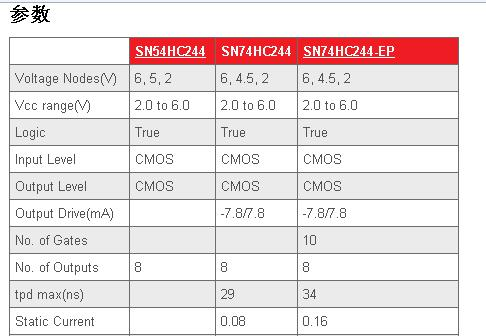

信息内容:说明 These octal buffers and line drivers are designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. The ’HC244 devices are organized as two 4-bit buffers/drivers with separate output-enable (OE)\ inputs. When OE\ is low, the device passes noninverted data from the A inputs to the Y outputs. When OE\ is high, the outputs are in the high-impedance state. 特性 Wide Operating Voltage Range of 2 V to 6 V High-Current Outputs Drive Up To 15 LSTTL Loads 3-State Outputs Drive Bus Lines or Buffer Memory Address Registers Low Power Consumption, 80-µA Max ICC Typical tpd = 11 ns ±6-mA Output Drive at 5 V Low Input Current of 1 µA Max dzsc/17/6600/17660025.jpg

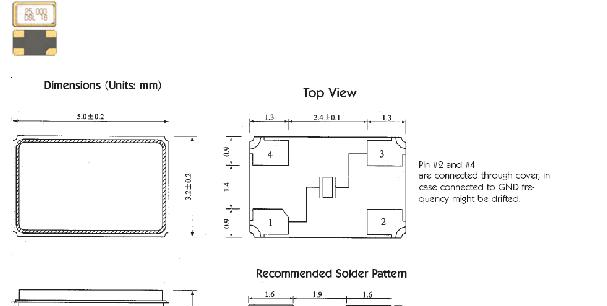

无源贴片晶振 5032 4p CPX-49SP 30MHZ

信息内容:无源贴片晶振 5032 4p CPX-49SP 30MHZ dzsc/17/6600/17660028.jpg